Технический вебинар: "Высокоуровневое проектирование на платформе Xilinx" 26 сентября в 10:00.

30.08.2019 14:05

1159

0

5.0

Приглашаем специалистов на бесплатный вебинар «Высокоуровневое проектирование на платформе Xilinx». Вебинар предназначен как для разработчиков, освоивших классический маршрут проектирования для ПЛИС, так для и программистов, желающих научиться программировать ПЛИС на С/С++. Так же приглашаются студенты-старшекурсники, интересующиеся методологиями проектирования на ПЛИС.

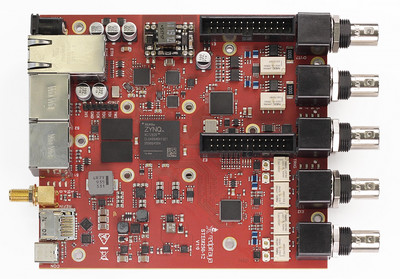

Долгие годы проектирование для ПЛИС было очень трудным делом, а многие этапы этого процесса напоминали белую и черную магию. Рисунок хорошо иллюстрирует один из методов работы специалистов по ПЛИС «старой закалки».

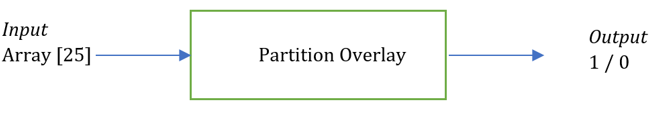

Существуют ли в наши дни методы и инструменты для упрощения и ускорения процесса разработки? Да, такие методы и инструменты существуют. Теперь вы можете выполнять проекты на ПЛИС, просто описывая их функциональность на С/С++. Это очень важный момент, поскольку теперь для проектирования на ПЛИС можно привлекать вместо «дорогих и дефицитных» FPGA-разработчиков обычных программистов, а сами проекты выполнять в несколько раз быстрее и дешевле. Кроме того, в рамках методологии высокоуровневого проектирования можно реализовывать на ПЛИС сложные алгоритмы, ранее написанные в виде программ для микропроцессоров/микроконтроллеров.

Компания Xilinx.Inc на данный момент имеет целых три инструмента высокоуровневого проектирования – Vivado HLS, SDSoC и SDAccel. Об их назначении, особенностях и эффективном применении вы узнаете на вебинаре. Главное внимание будет уделено продукту Vivado HLS, поскольку остальные перечисленные выше инструменты являются развитием данного продукта.

ПРОГРАММА ВЕБИНАРА:

Вебинар состоится 26 сентября в 10:00.

Повтор вебинара 2 октября в 14:00. Время московское.

УЧАСТИЕ В ВЕБИНАРЕ БЕСПЛАТНОЕ ПОСЛЕ ПРЕДВАРИТЕЛЬНОЙ РЕГИСТРАЦИИ.

Зарегистрироваться на вебинар

Технический вебинар: "Высокоуровневое проектирование на платформе Xilinx" 26 сентября в 10:00.

Существуют ли в наши дни методы и инструменты для упрощения и ускорения процесса разработки? Да, такие методы и инструменты существуют. Теперь вы можете выполнять проекты на ПЛИС, просто описывая их функциональность на С/С++. Это очень важный момент, поскольку теперь для проектирования на ПЛИС можно привлекать вместо «дорогих и дефицитных» FPGA-разработчиков обычных программистов, а сами проекты выполнять в несколько раз быстрее и дешевле. Кроме того, в рамках методологии высокоуровневого проектирования можно реализовывать на ПЛИС сложные алгоритмы, ранее написанные в виде программ для микропроцессоров/микроконтроллеров.

Компания Xilinx.Inc на данный момент имеет целых три инструмента высокоуровневого проектирования – Vivado HLS, SDSoC и SDAccel. Об их назначении, особенностях и эффективном применении вы узнаете на вебинаре. Главное внимание будет уделено продукту Vivado HLS, поскольку остальные перечисленные выше инструменты являются развитием данного продукта.

ПРОГРАММА ВЕБИНАРА:

- Технология высокоуровневого проектирования (HLS) – что это такое?

- Технологии HLS от Xilinx, основные документы.

- Обзор Vivado HLS, SDSoC и SDAccel.

- Vivado HLS – назначение и основные функции.

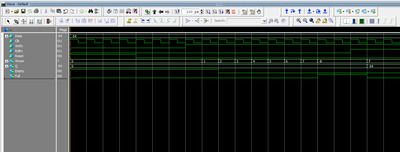

- Этапы проектирования в Vivado HLS.

- Методика портирования разработанного для процессоров C/C++ кода в ПЛИС Xilinx.

- Методы и приемы повышения производительности генерируемого кода.

Вебинар состоится 26 сентября в 10:00.

Повтор вебинара 2 октября в 14:00. Время московское.

УЧАСТИЕ В ВЕБИНАРЕ БЕСПЛАТНОЕ ПОСЛЕ ПРЕДВАРИТЕЛЬНОЙ РЕГИСТРАЦИИ.

Зарегистрироваться на вебинар