Руководство по преобразованию кернела HLS 300 MHz на RTL 500 MHz для Vivado 2020.2

На конференции FPGA-Systems 2020 был представлен доклад "Особенности реализации RTL и Vivado HLS kernel для ускорителей ALVEO" в котором был представлен учебный пример собранный с использованием Vitis 2020.1. В системе разработки Vitis 2020.2 несколько изменился состав проектов и порядок работы и это потребовало изменение примера.

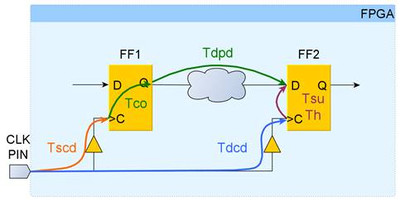

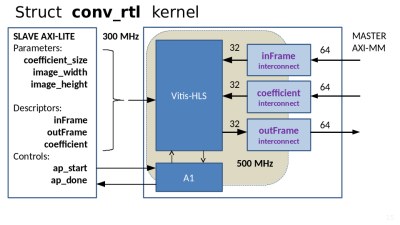

Пример основан на учебном проекте Xilinx и показывает как можно произвести свёртку видео на ускорителе Alveo. В исходном примере Xilinx показано как разработать кернел на Vitis-HLS. В преобразованном примере HLS кернел помещается внутрь RTL кернела и это позволяет поднять тактовую частоту работы с 300 МГц до 500 МГц.

.

.

Пример включает подробное руководство как создать проект Vitis-HLS, собрать IP Core, созадать проект Vitis и RTL кернел. Пример показывает как работать с Vitis в режиме GUI.

Ссылка на пример: https://github.com/dsmv/Vitis_OpenCL_Tutorials/tree/main/01-convolution-dataflow-rtl-500MHz